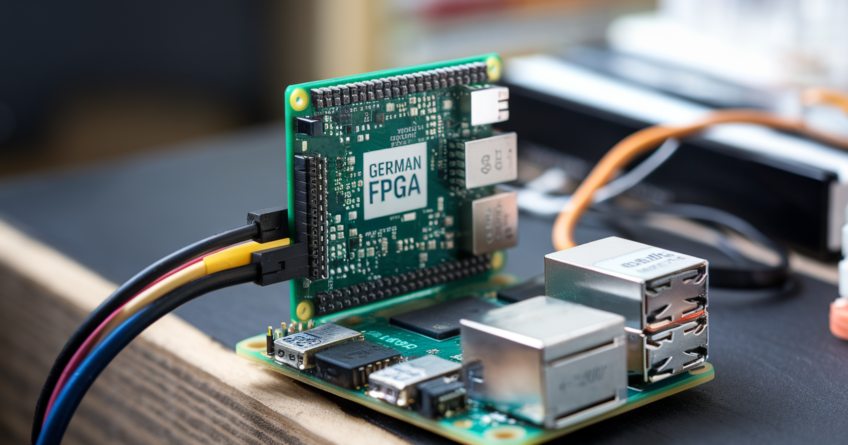

Cologne Chip, a small German outfit with big “we’re doing this our way” energy, just dropped its GateMate A1 FPGA onto a module designed to fit Raspberry Pi Compute Module 5 (CM5) I/O boards. Translation: they’re trying to smuggle reconfigurable logic into one of the most familiar hardware ecosystems on the planet, without forcing you to swallow the usual proprietary FPGA toolchain misery.

If you’ve ever flirted with FPGAs and bounced off because the software felt like it was built in 2006 for a defense contractor with infinite patience, Cologne Chip is aiming straight at you. Their pitch has two hooks: the chip is designed in Europe, and the workflow leans on open-source tools. That combo is a direct shot at the status quo, where the silicon might be affordable but the tooling is a walled garden with a toll booth.

The move also lands at a moment when FPGAs aren’t just for telecom racks and factory floors. People are using them for edge computing, data capture, robotics, video pipelines, and fast prototyping, stuff that used to be “microcontroller territory” until timing, latency, or weird I/O requirements showed up and ruined your weekend.

A CM5-shaped Trojan horse for FPGA adoption

The key decision here isn’t some exotic spec sheet flex. It’s packaging. Cologne Chip soldered the GateMate A1 onto a module meant to slot into carrier/I/O boards built for the Raspberry Pi Compute Module 5.

For Americans who don’t live in Raspberry Pi land: the Compute Module line is the “serious” Pi. It’s meant for products and industrial builds, processor and memory on a compact module, then you plug it into a carrier board that breaks out USB, PCIe, Ethernet, GPIO, and whatever else you need. It’s how you go from “prototype on a bench” to “thing you can actually ship” without redesigning everything from scratch.

So if an FPGA module can ride that same mechanical and electrical ecosystem, you’re not starting from zero. Power regulation, connectors, board outlines, mounting, those problems are often already solved by the CM5 carrier board universe. That can shave real engineering time and cost, which is the part nobody budgets for when they say, “Let’s just add an FPGA.”

But there’s a catch, and it’s not a small one: I/O is everything with FPGAs. The article’s source material doesn’t spell out the full electrical details, pin routing, voltage standards, signal integrity constraints, reference schematics. That’s the stuff integrators will demand before they bet a project on it. “Fits the slot” is nice. “Works reliably at speed” is the whole game.

Open-source FPGA tools: the real fight is software, not silicon

Cologne Chip is also leaning hard on “open source tools,” and that’s not marketing fluff in FPGA world, it’s a declaration of war against the traditional model.

Most FPGA vendors still push heavyweight proprietary suites: licensed, OS-picky, version-fragile, and about as friendly to modern CI/CD as a fax machine. If you’re a software-forward team trying to automate builds, run reproducible toolchains, and keep projects portable, those environments can be a deal-breaker.

Open source can mean a lot of things, though. Some companies open a few helper libraries and call it a day. The question that matters is blunt: can you run the full flow, synthesis, place-and-route, bitstream generation, without proprietary tools? The documentation referenced in the French piece doesn’t fully nail that down. Cologne Chip’s intent is clear, but the details will decide whether this is liberation or just “open-ish.”

And then there’s the unglamorous part: examples, reference designs, basic IP blocks, simulation support, and docs that don’t read like they were translated by a committee. A cheap FPGA with a painful bring-up experience stops being cheap fast.

“Affordable” isn’t a price tag, it’s total pain over time

Every new FPGA entrant calls itself affordable. Fine. But the chip price is only one line item. The real cost is the board, the power design, the integration work, and the engineering hours you burn getting from “blinky LED” to “this actually ships.”

By targeting CM5 I/O boards, Cologne Chip is trying to win on total cost of implementation: fewer custom hardware headaches, faster validation, and a clearer path from prototype to something that looks like a product.

What’s still missing from the public-facing pitch is the kind of hard data engineers will immediately ask for: logic capacity, on-chip memory, dedicated blocks, PLLs, power draw, I/O performance. Without those numbers, you can’t honestly compare it to the usual suspects. Right now, the strategy reads like: make adoption easy first, let the community decide if the silicon is “enough.”

A European FPGA poking the American-and-Asian giants

There’s also a geopolitical subtext here, whether Cologne Chip says it out loud or not. The FPGA market has long been dominated by massive players, mostly American, with plenty of Asian manufacturing gravity, paired with proprietary toolchains and deep IP libraries.

Europe has been pushing harder on tech sovereignty since the early-2020s supply chain chaos, and a “designed in Europe” FPGA is part of that broader industrial mood. No, it doesn’t magically mean the whole supply chain is European, fabs and passives are global. But it does mean another architecture, another vendor, another option when procurement teams start sweating single-source risk.

The problem is credibility. The big vendors have decades of tooling maturity, huge communities, and IP catalogs that solve problems before you even know you have them. Cologne Chip’s differentiator here looks less like raw performance and more like developer experience: CM5-friendly hardware plus an open-source-leaning flow.

If they can back that up with solid docs, stable tools, and real support, especially around timing closure and errata, this could become a legit on-ramp for teams who want FPGA capability without the usual vendor lock-in hangover.

Quick answers (because everyone asks the same three things)

What do you gain from an FPGA module compatible with Raspberry Pi CM5 I/O boards?

You get mechanical and electrical familiarity, carrier boards already exist, so prototyping can move faster and cost less.

Why do open-source tools matter for an FPGA?

Because toolchains decide your productivity. Open flows can be automated, audited, and reproduced without license drama.

Does this replace a Raspberry Pi CM5?

No. The CM5 runs Linux and applications. The FPGA implements custom hardware logic, usually as a companion, not a substitute.

Frequently Asked Questions

What does an FPGA module compatible with Raspberry Pi CM5 I/O boards provide?

It simplifies mechanical and electrical integration into an existing ecosystem of carrier boards, which can speed up prototyping and reduce engineering cost.

Why does using open-source tools matter for an FPGA?

An open-source flow can improve build reproducibility, automation, and transparency in the generation process, while reducing reliance on proprietary licenses.

Does the GateMate A1 module replace a Raspberry Pi CM5?

No. An FPGA and a Compute Module serve different roles: the CM5 runs an operating system and applications, while the FPGA is used to implement reconfigurable hardware logic, often as a complement.